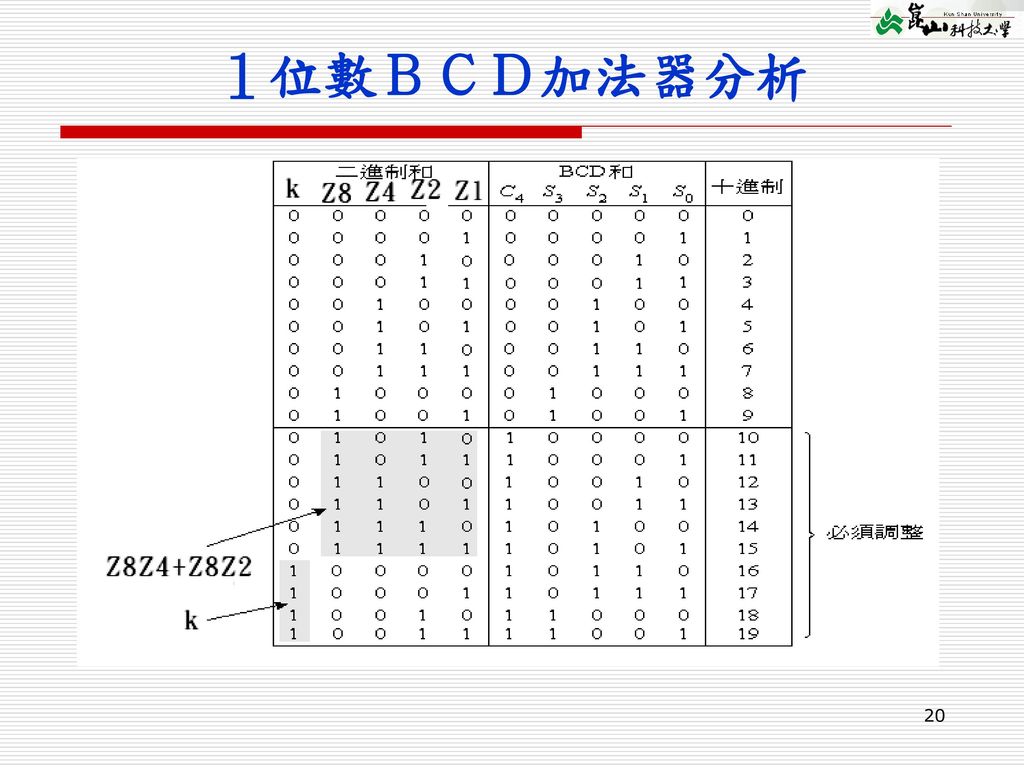

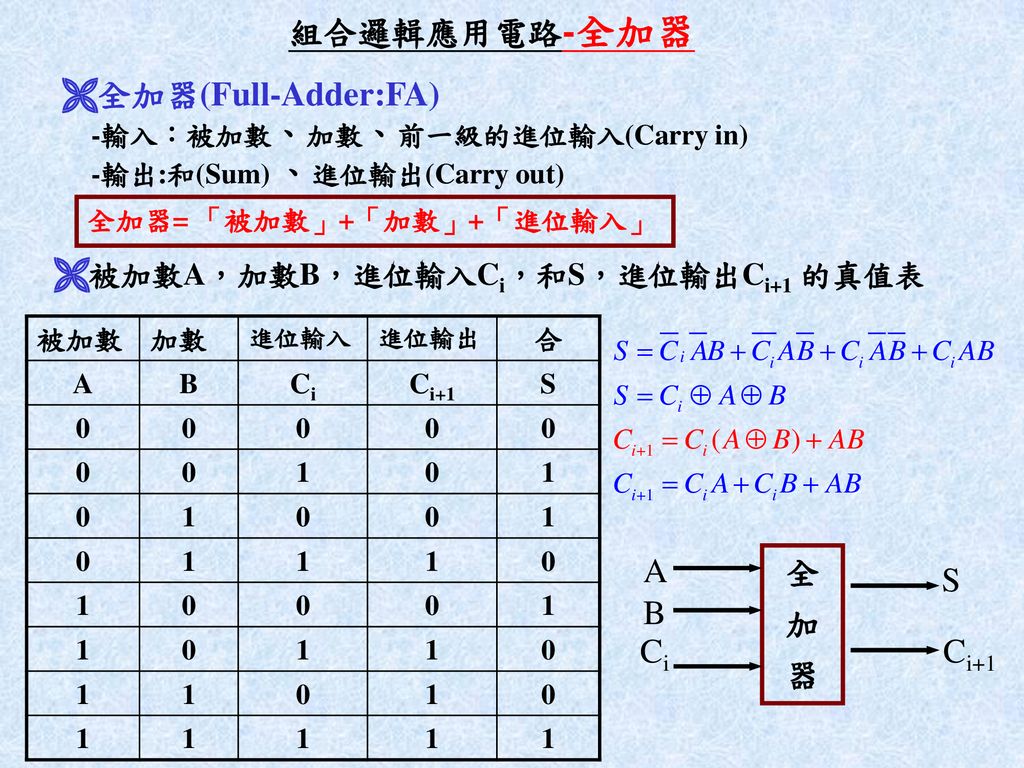

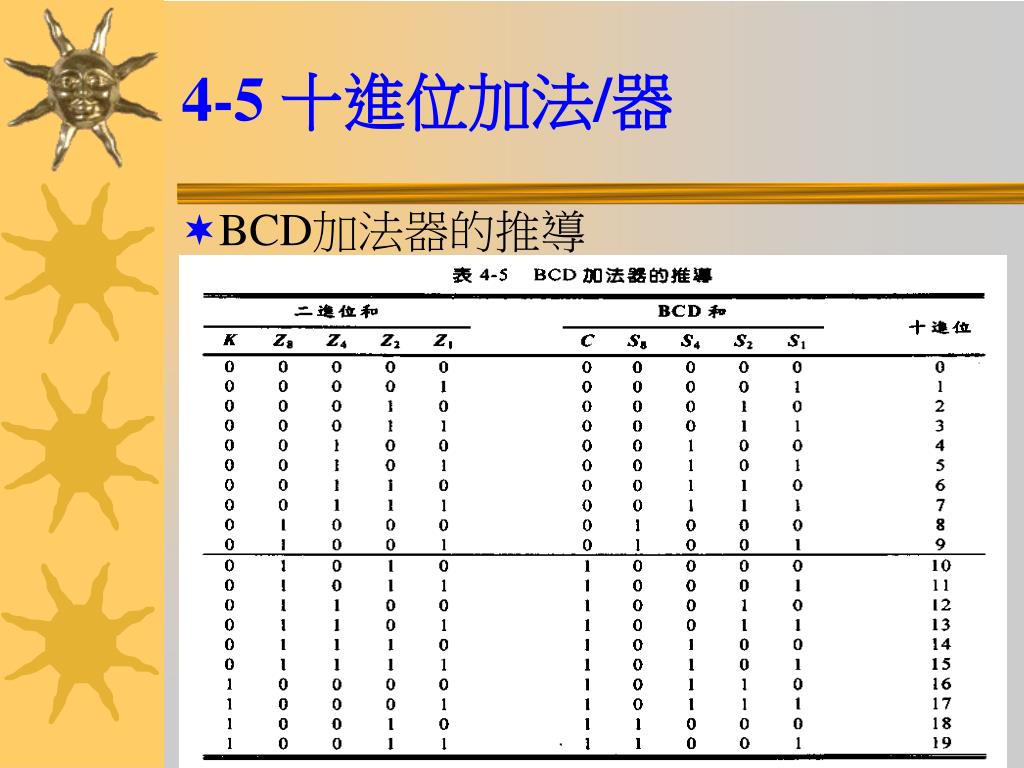

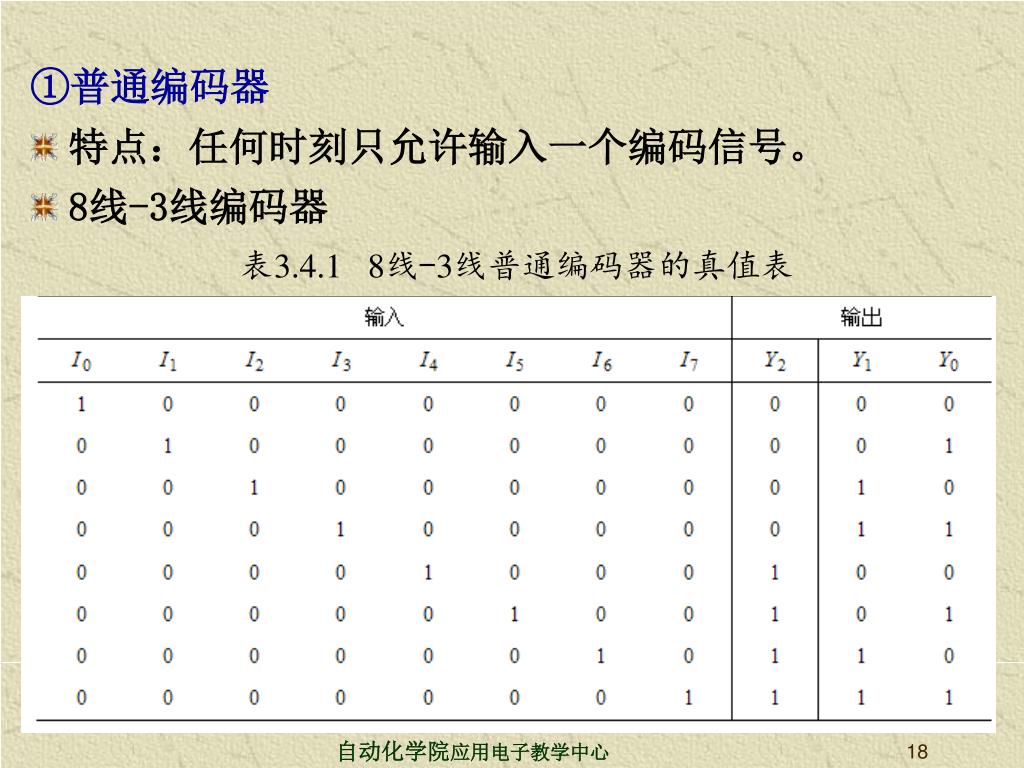

实验七 4选1多路选择器设计实验,如何下载 54在 三 人 表 决 器 中 三 个 人 分 别 用 手 指 拨 动 开 关 s w 1 、s w 2 、s w 3 来 表 示 自 己 的 意 愿 ,如 果 对 某 决 议 同 意 , 各人就 把自 己的 指 拨开关 拨到 高电 平(上 方),不 同意 就把自 己 的 指 拨 开 关 拨 到 低 电 平 ( 下 方 ) 。1 1 0 6 0 1 1 1 1 7 1 1 根据上面的真值表,可以设计出电路图: 将38译码器的输出out(1、2、4、7)作为一个4输入的或门的输入,或门的输出作为加法器的和;将38译码器的输出out(3、5、6、7)作为一个4输入的或门的输入,或门的输出作为加法器的进位输出。

基于multisim的电子系统设计 仿真与综合应用 第2版 Eda技术实用丛书 第二部分应用篇

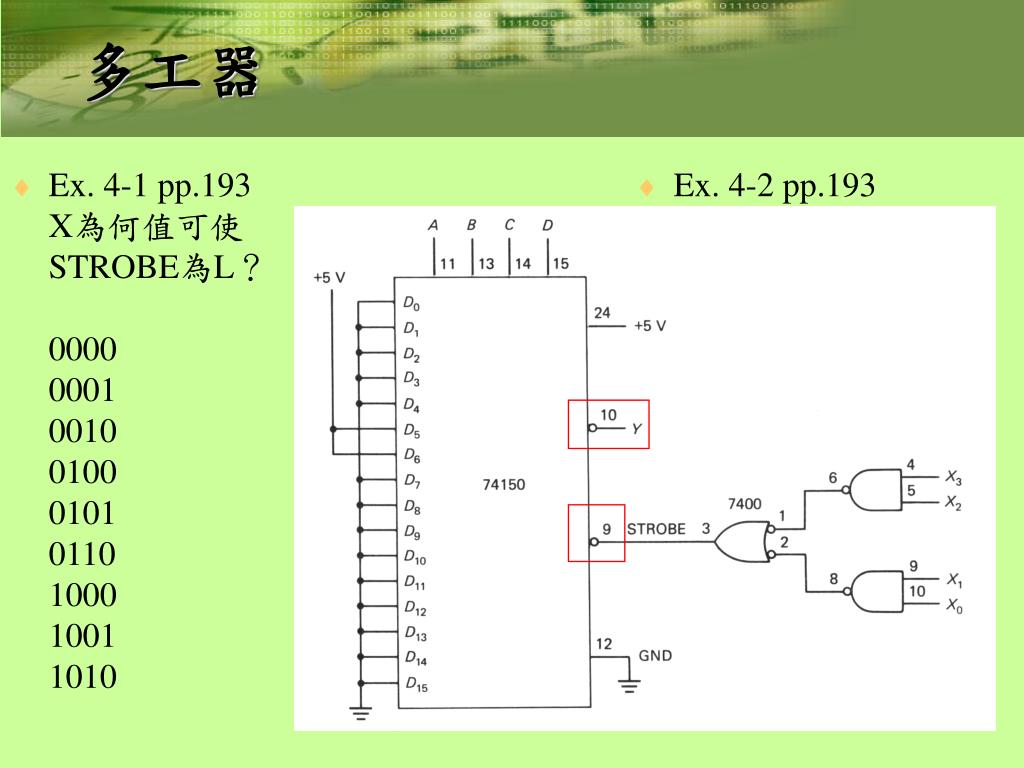

8对1多工器真值表

8对1多工器真值表-实验七 4选1多路选择器设计实验,如何下载 ;两个多项集若要相等,它们必须为相同类型、相同长度,并且每对相应的元素都必须相等(例如, 1,2 == (1,2) 为假值,因为类型不同)。 对于支持次序比较的多项集,排序与其第一个不相等元素的排序相同(例如 1,2,x

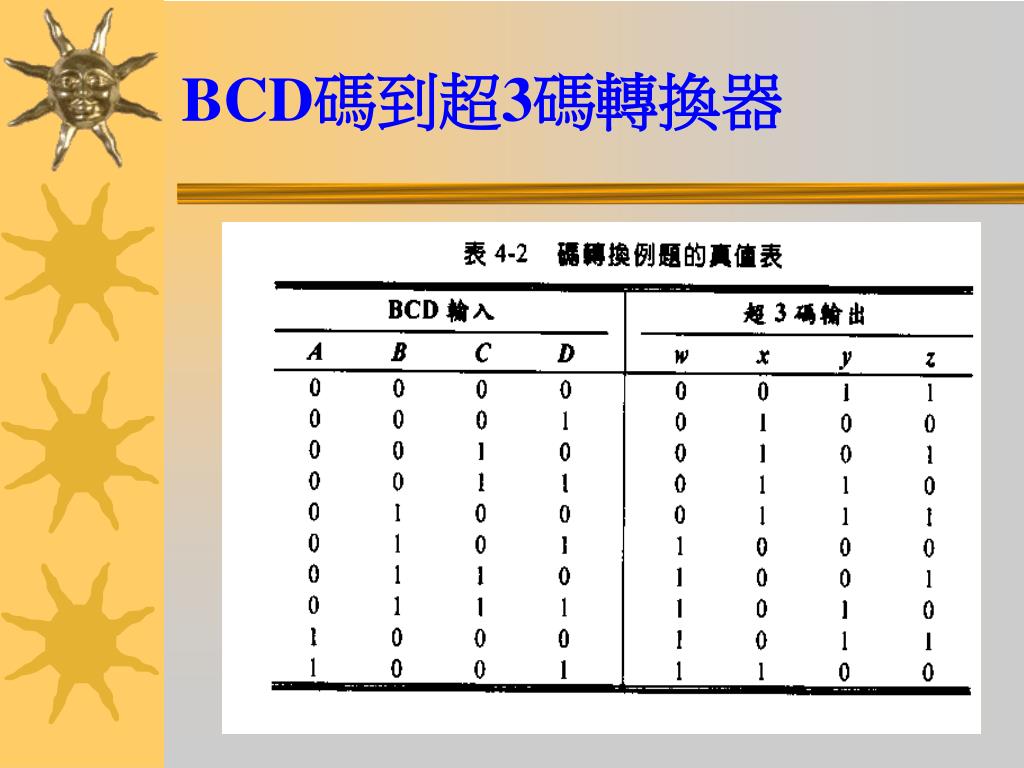

第六章 布林代數 布林代數表示 布林代數基本運算定理 布林代數化簡 Ppt Download

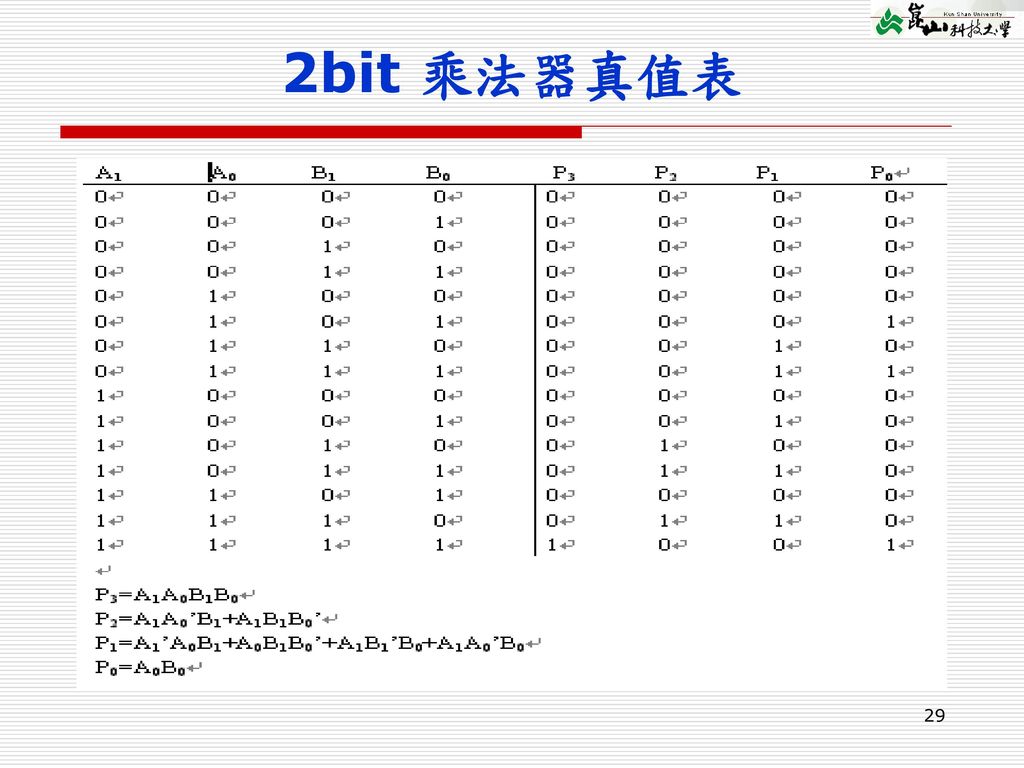

知乎,中文互联网最大的问答社区和创作者聚集的原创内容平台,于 11 年 1 月正式上线,以「让人们更好地分享知识、经验和见解,找到自己的解答」为品牌使命。知乎凭借认真、专业、友善的社区氛围、独特的产品机制以及结构化和易获得的优质内容,聚集了中文互联网科技、商业、影视、时尚表1 符合性因子(1) 2 rde难点分析与应对方案 rde试验将车辆尾气监测从实验室扩展到了实际驾驶路面,车辆实际使用环境复杂,影响rde结果的因素更多,如下表2所示。 表 2 实际行驶污染物排放(rde)影响因素Verilog实现乘法器以下介绍两种实现乘法器的方法:串行乘法器和流水线乘法器。1)串行乘法器 两个N位二进制数x、y的乘积用简单的方法计算就是利用移位操作来实现。其框图如下: 其状态图如下: 其实现的代码如下: modulemulti_CX(clk, x, y, result);

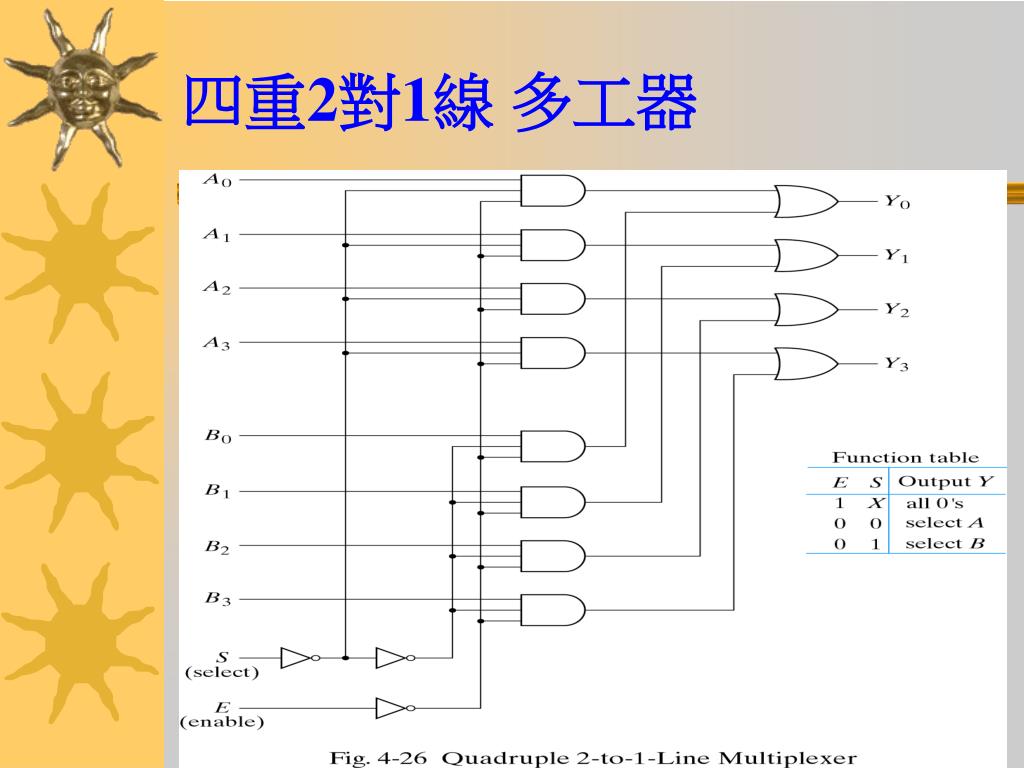

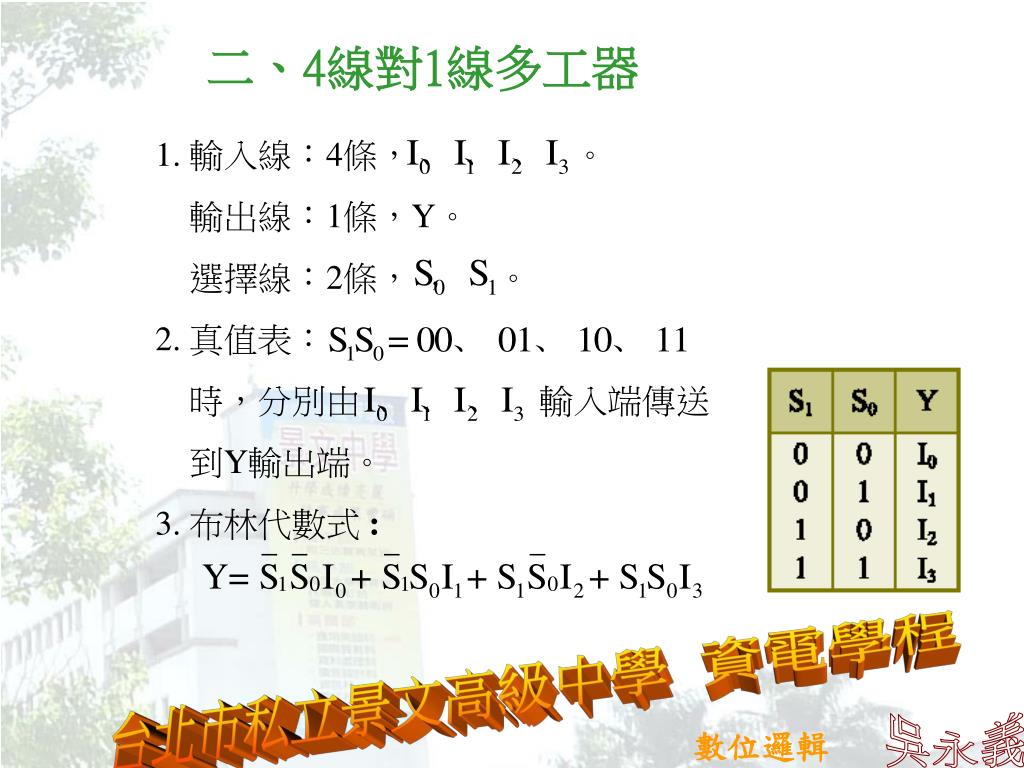

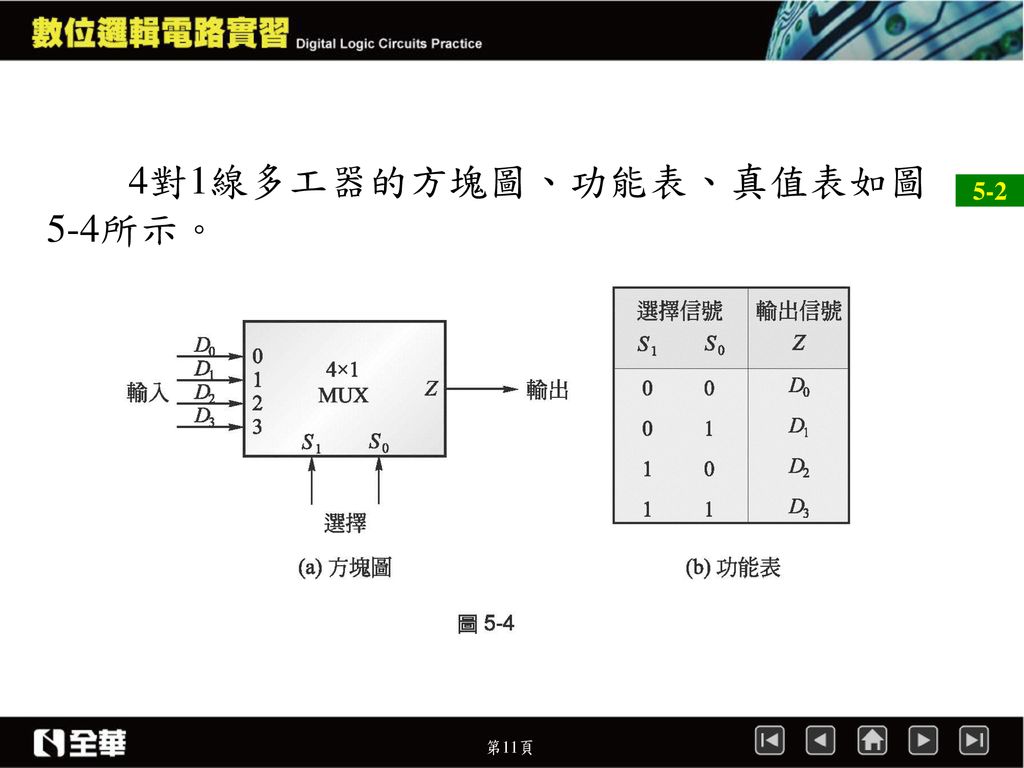

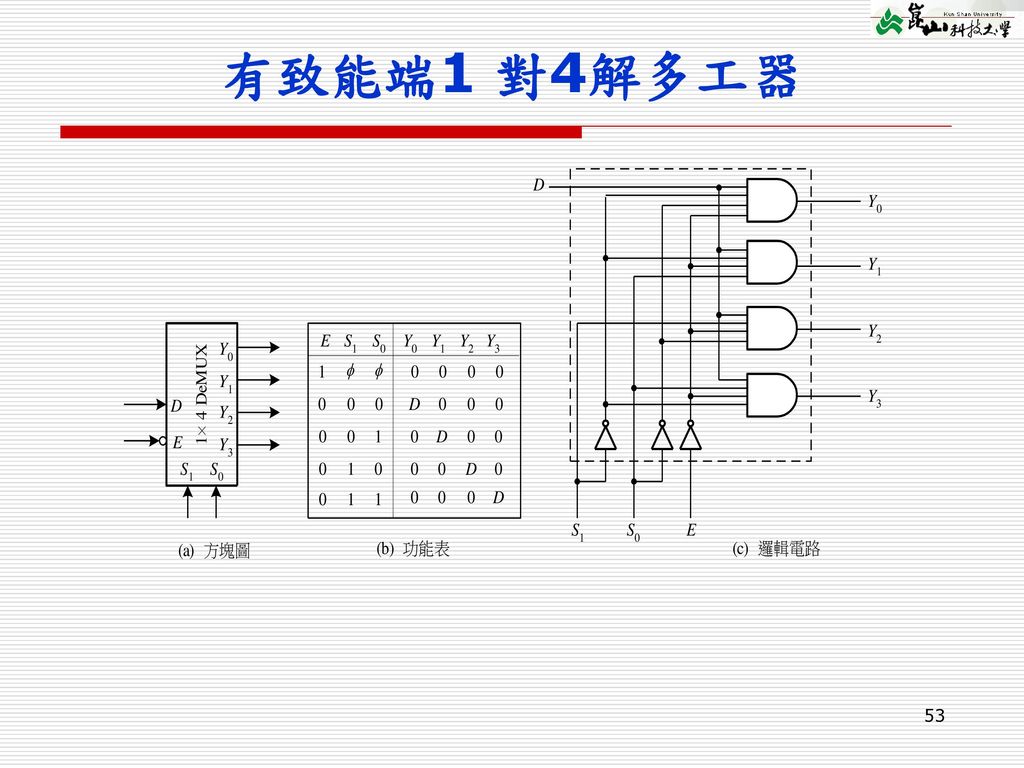

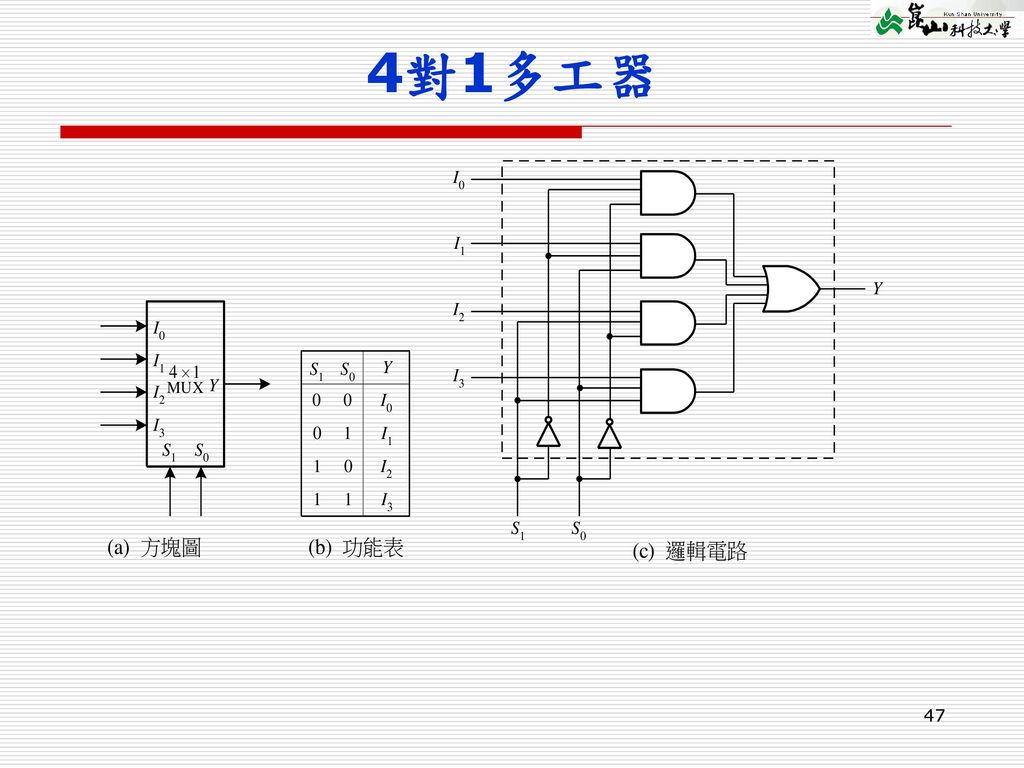

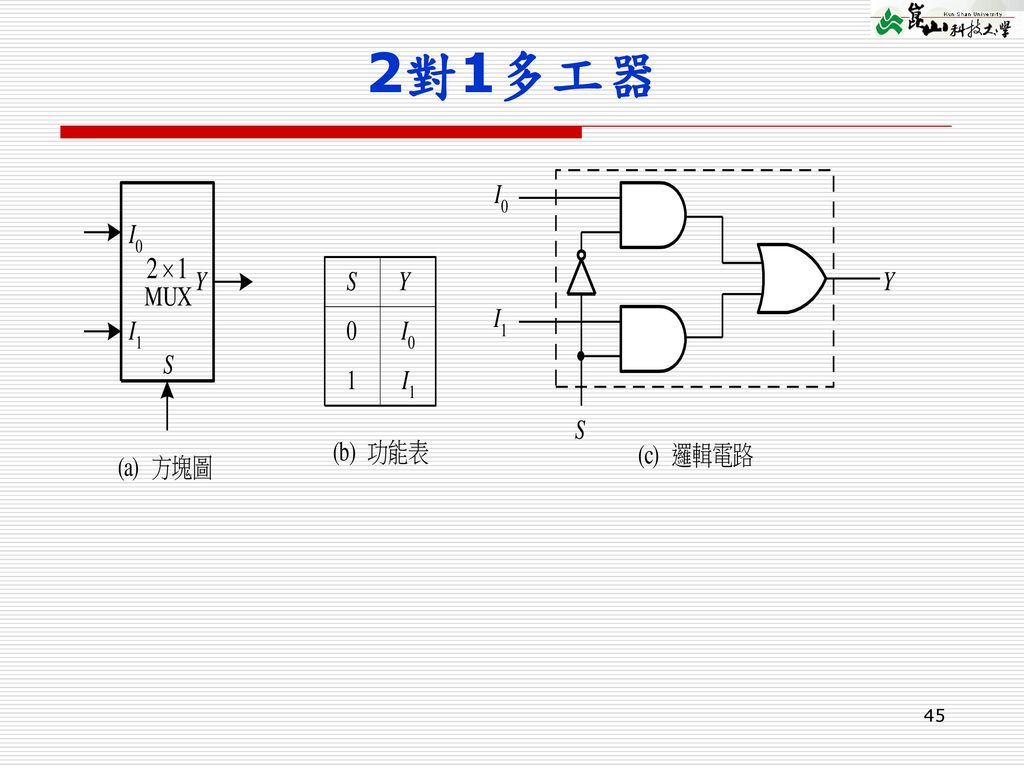

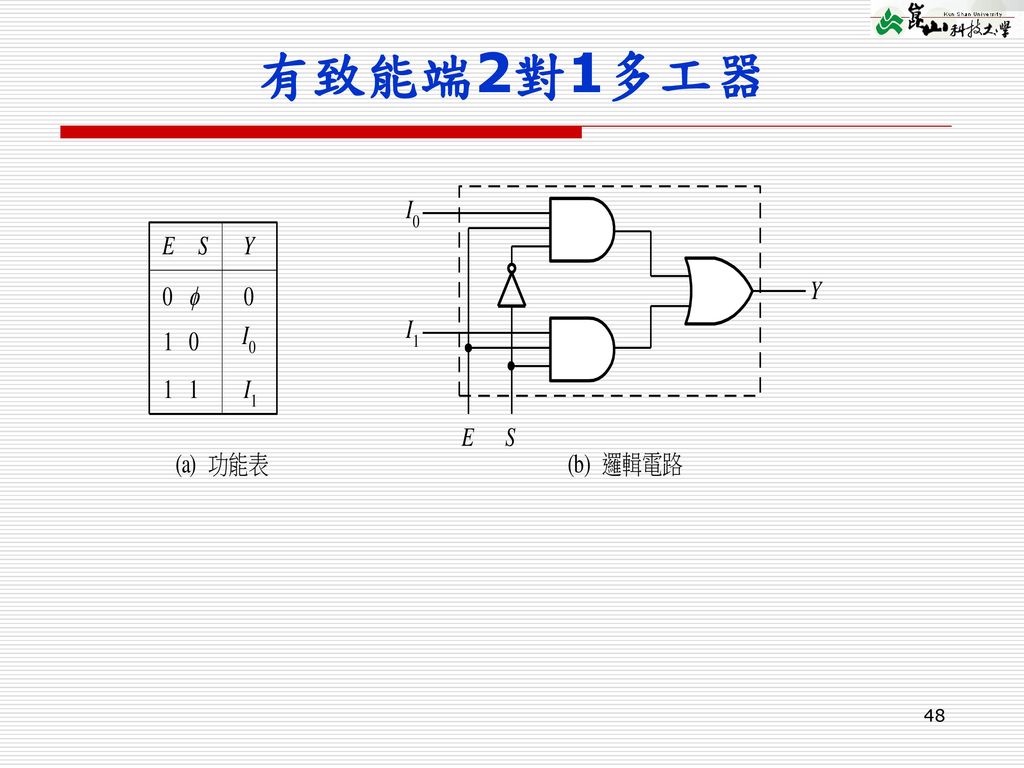

题解 表39 题解表310 填入卡诺图,并圈"1"合并,如题解图325 所示,得到f acac bcabd acd bcd abd 311分析题图38 所示由集成3 线8 线译码器ct 构成的电路,写出 输出f 的逻辑函数表达式,列出f 的真值表,并找出在控制信号k 的作用下, 该电路的功能。这个真值表显示,当 = ,那么 = ;而当 = ,则 = 。 在具体的电路中,实现一个这样的2选1数据选择器需要2个与门、一个或门和一个非门。 更大型的数据选择器也较常见,而且正如上面描述的, 个输入引脚需要 个选择引脚。 其他常见的类型有4选1、8选1和16选1等。74HC153双4选一数据选择器数据手册doc,74HC153双4选一数据选择器数据手册 特点: 1它是一个双4选一数据选择器,即它包含两个完全相同的4选一数据选择器。 2有8个数据输入端,相互独立,2 个非反相数据输出端,,即2 个数据输入端是相互独立的 3两个数据选择器有公共的地址输入端。

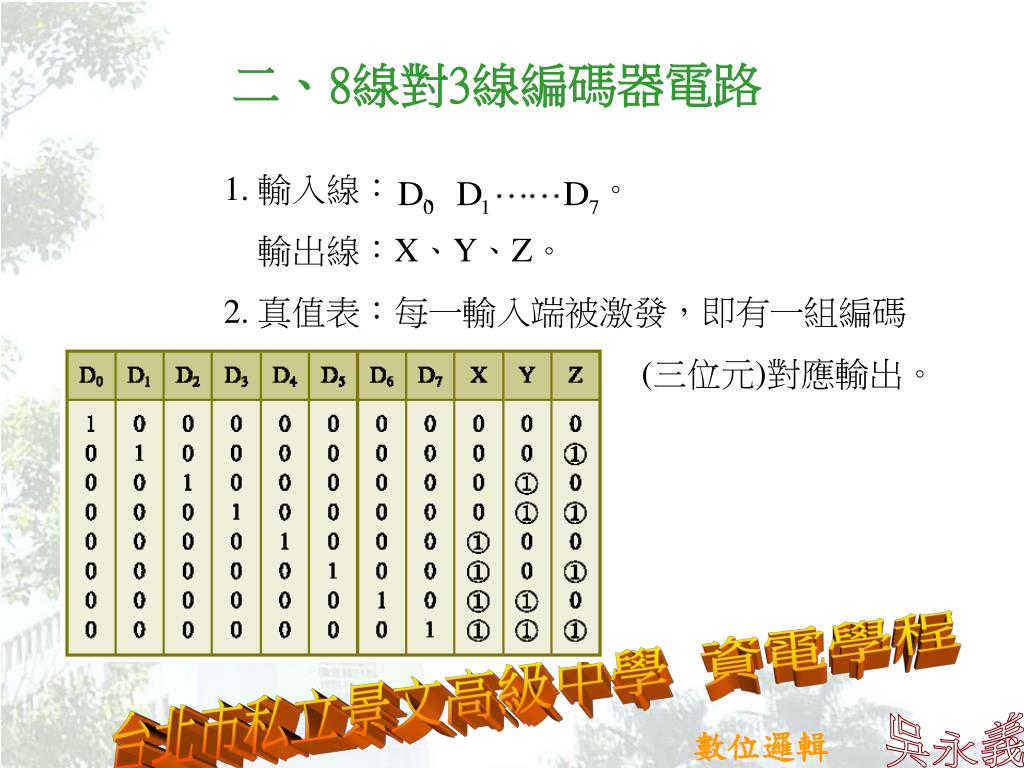

数电试题与答案(五套)doc,PAGE PAGE 1 《数字电子技术基础》试题一 填空题(22分 每空2分) 1、 , 。 2、JK触发器的特性方程为: 。 3、单稳态触发器中,两个状态一个为 态,另一个为 态多谐振荡器两个状态都为 态, 施密特触发器两个状态都为 态 4、组合逻辑电路的输出仅仅只与该时刻的 有关,而与关键词: 热工仪表 摘要: 本文围绕常见热工仪表,介绍了选型、安装使用的基础知识。 1、 测量误差 概念 11、误差的分类 按误差数值表示的方法分为:绝对误差、相对误差、引用误差; 按误差出现的规律分为:系统误差(规律误差)、随机误差(偶然误差)、疏忽误差(粗大误差) 12、真值与线译码器74ls138逻辑功能 表323线-8 线译码器74ls138 功能表 由三位二进制译码器真值表(表1)得实验中 11感谢观看本文谢谢 标签标题 16 线译码器74ls138 实现了逻辑功能。

Ppt 第四章powerpoint Presentation Free Download Id

數位邏輯設計與實習ch04 組合邏輯電路設計 Ppt Download

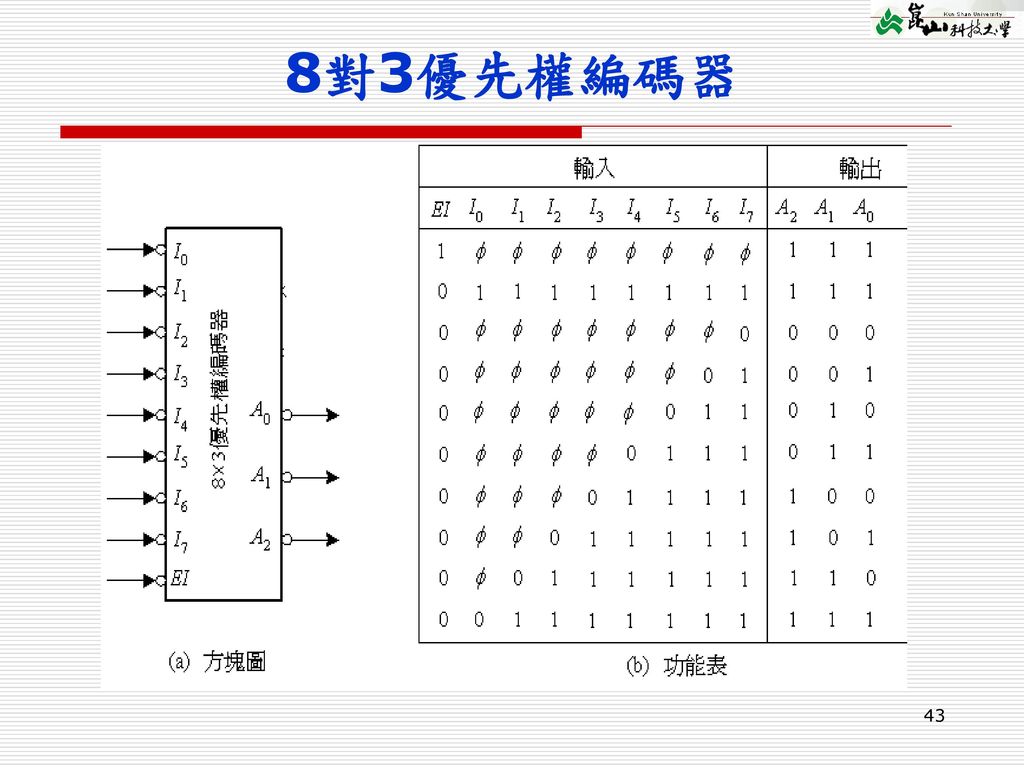

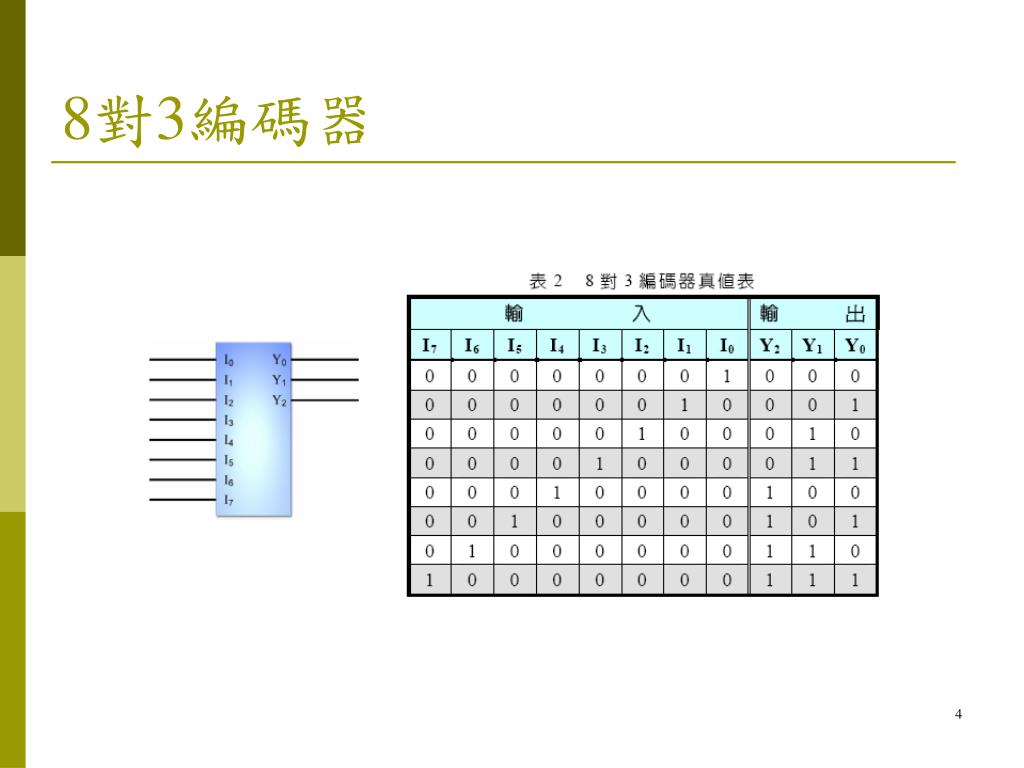

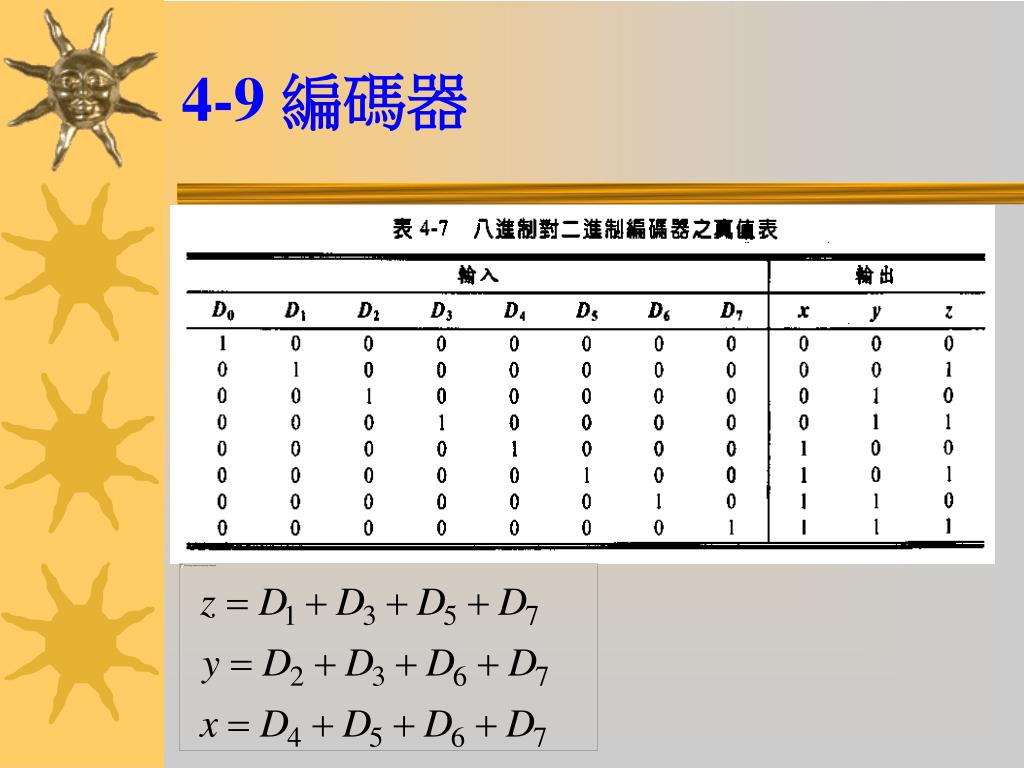

38译码器真值表讲解从这个名字来剖析,三八译码器,就是把 3 种输出形态翻译成 8 种输入形态。从图 315所能看出来的,74hc138 有 1~6 一共是 6 个输出引脚,然则个中 4、5、6 这三个引脚是使能引脚。使能引脚和我们前边讲 74hc245 的 oe 引脚是一样的对Student、Course和Sc表,按以下要求用TSQL语句建立触发器 1 在Student表上建立事后插入触发器,触发器功能为显示插入的记录和"插入成功"提示信息。 2 在Student表上建立事后更新触发器,触发器功能为显示更新前和更新后的记录及"更新成功"提示信息。 38选1数据选择器的型号为、74ls151、和74ls152这几种。 扩展资料: 8选1数据选择器数据选择器的典型应用: 采用8选1数据选择器74ls151可实现任意三输入变量的组合逻辑函数。作出函数f的功能表,将函数f功能表与8选1数据选择器的功能表相比较,可知: 1、将

基于multisim的电子系统设计 仿真与综合应用 第2版 Eda技术实用丛书 第二部分应用篇

数字电路基础知识 六 Fpga的逻辑实现 结构和原理 摆渡沧桑 Csdn博客 Fpga通过什么实现逻辑功能

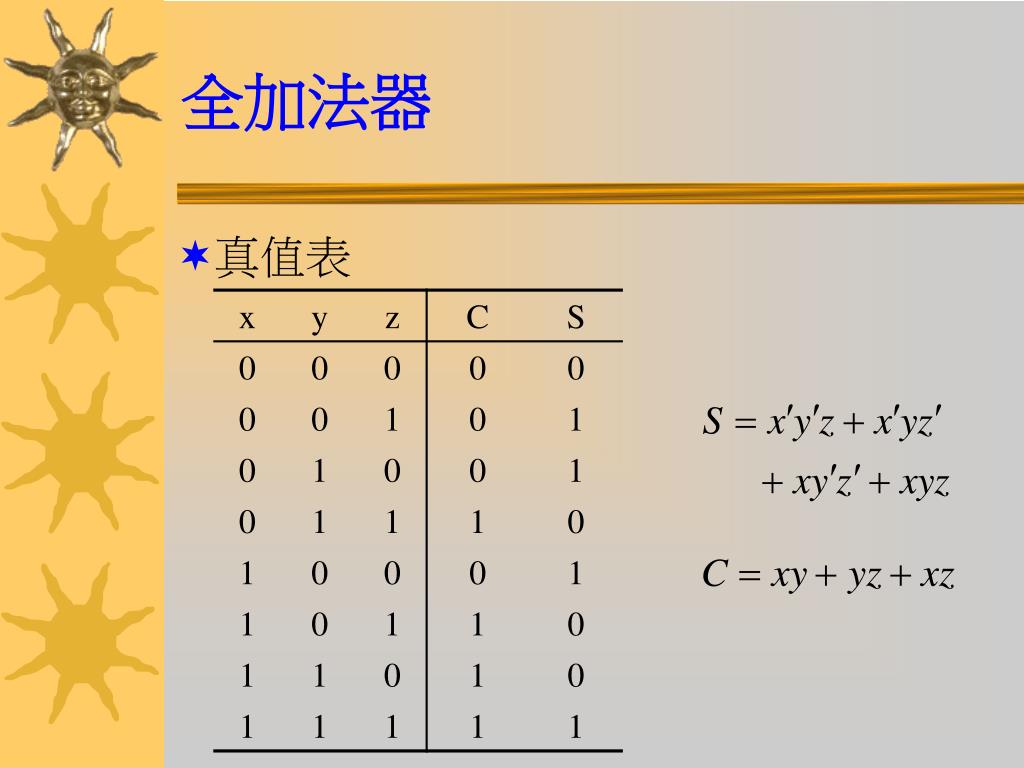

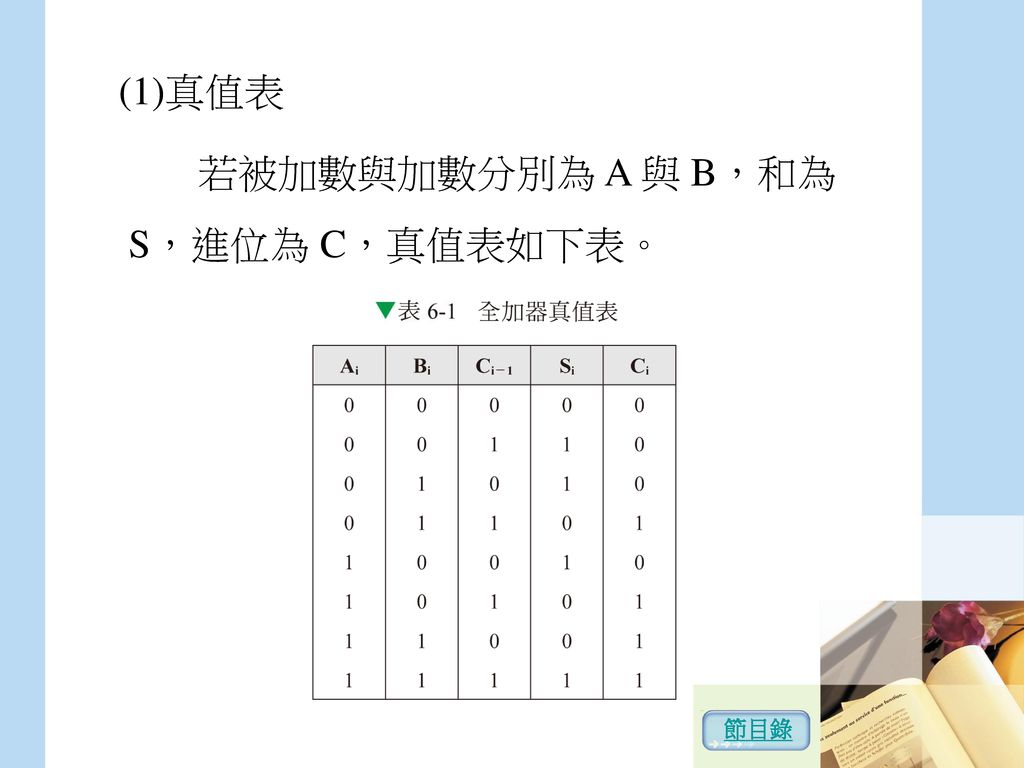

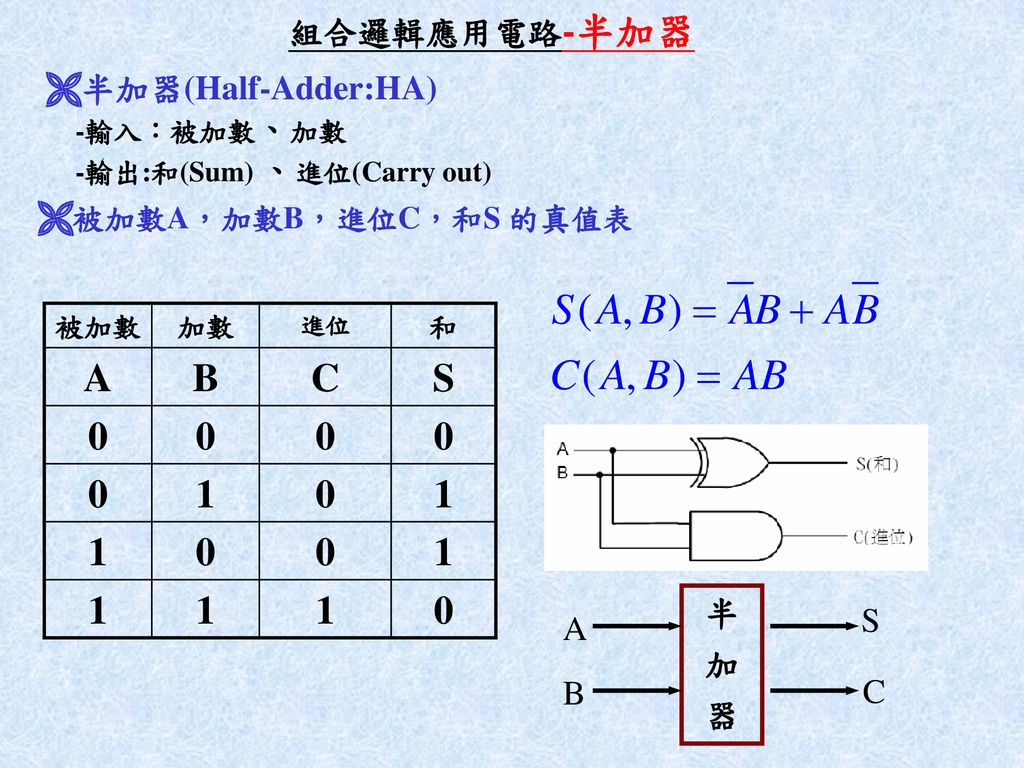

1 4 42全加器原理 421 一位全加器的设计与原理 一位全加器的原理图如下: 图 41 一位全加器原理图 一位全加器的程序设计: ENTITY adder1 IS PORT(a,b,cinIN STD_LOGIC;实验七 4选1多路选择器设计实验,如何下载 ;并行查询(Parallel Query)利用多核CPU的并行处理能力,以8核32 GB的 PolarDB MySQL 集群版 为例,示意图如下所示。 前提条件 PolarDB 集群版本需为 PolarDB MySQL 80且Revision version为或以上,您可以通过 查询版本号 确认集群版本。 应用场景

Ppt 數位邏輯實習powerpoint Presentation Free Download Id

數位邏輯設計與實習ch04 組合邏輯電路設計 Ppt Download

数显工频表、传感器专用数显表、频率转速线速表、电子计数器、数显温度温控器、智能时间继电器 公司简介 柳州超尔崎电子有限公司座落在具有二千多年历史的古城广西工业重镇柳州市。 超尔崎公司先后推出三位半、四位、四位半、五位数显(真现在写出全加器和38译码器的综合真值表 : (a/a 试用3线8线译码器74ls138和门电路实现下面多输出逻辑函数 用74ls138译码器设计一个控制电路对三台设备进行控制,当设备出故障时由不同的指示灯进行指示这个真值表显示,当 = ,那么 = ;而当 = ,则 = 。 在具体的电路中,实现一个这样的2选1数据选择器需要2个与门、一个或门和一个非门。 更大型的数据选择器也较常见,而且正如上面描述的, 个输入引脚需要 个选择引脚。 其他常见的类型有4选1、8选1和16选1等。

中国光学

Ppt 第四章powerpoint Presentation Free Download Id

对这款表对一切要求,都要建立在99包邮的基础上。 三、什么是TRMS和"显示位数": 21 TRMS真有效值: "真正有效值"之意,英文为"True Root Mean Square",也称为真均方根值,真有效值对应平均响应值。实验七 4选1多路选择器设计实验,如何下载 54ARCHITECTURE dataflow OF adder1 IS SIGNAL tmpSTD_LOGIC;

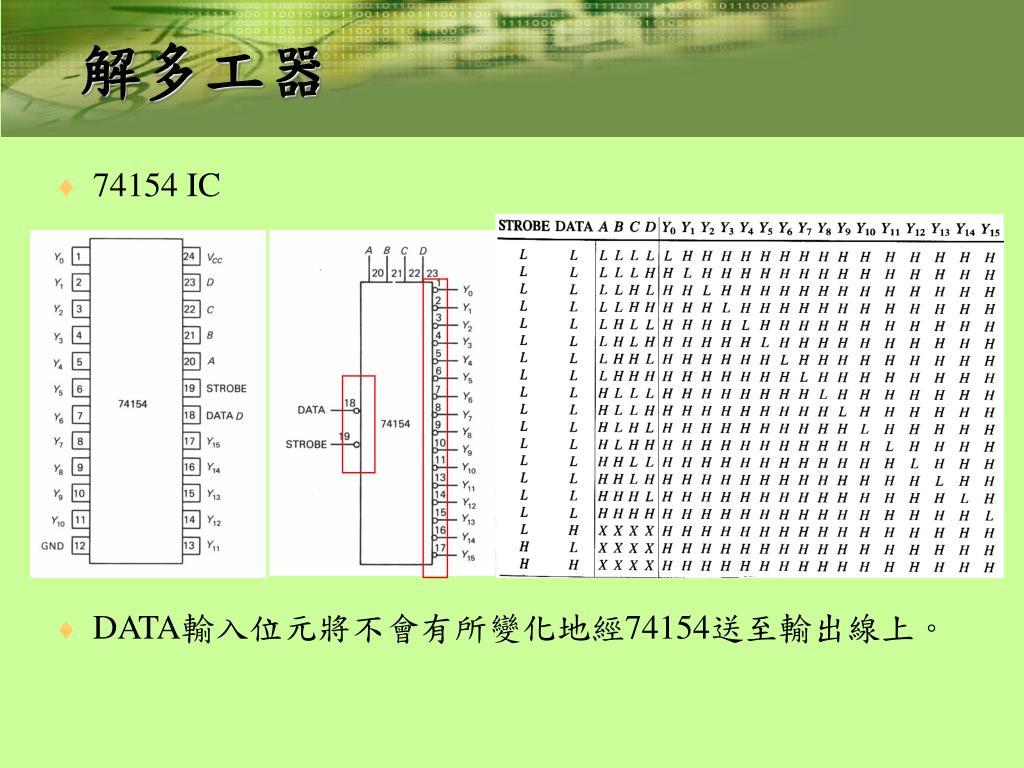

解碼器 維基百科 自由的百科全書

Ppt 吳永義powerpoint Presentation Free Download Id

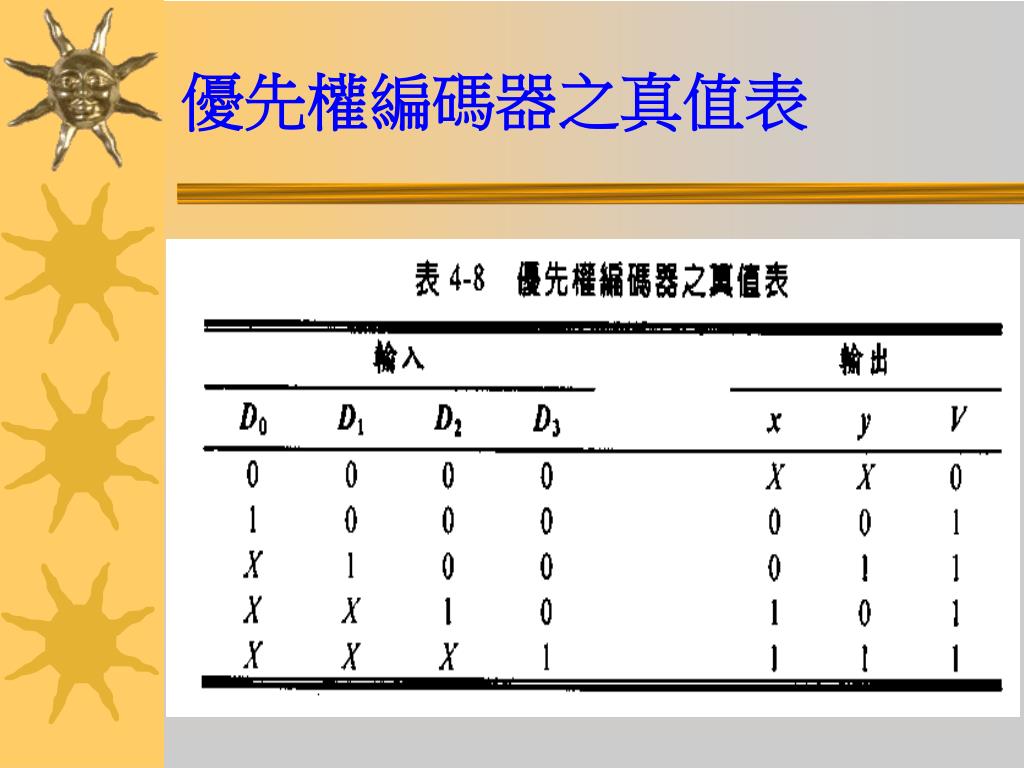

用8选1的mux实现逻辑函数 8选1mux的型号为,对将函数写成最小项形式并分配系数m0和m6接低其余接高。 8 选1实现 使用8选1数据选择器实现多输入逻辑函数5 二选一数据选择器 逻辑函数 只有在sel=1,且a=1时,y=1 真值表 内部逻辑 2集成电路74ls147的真值表需要背吗?如果需要怎么记?试卷 使用编码器74ls147,如何进行对十进制数0编码 3;74ls192真值表 根据设计要求,需要两片74ls192 构成100 进制减计数器。由功 能真值表可知,只需将个位74ls192 的借位输出端bo 与十位74ls192 的cpd 即可实现100 进制减计数。值得注意的是,要使其实现减计数, cpu 端口必须接高电平。 计数器的时钟脉冲由秒脉冲电路

Java中9种常见的cms Gc问题分析与解决 美团技术团队

數位邏輯設計與實習ch04 組合邏輯電路設計 Ppt Download

多位加法器的构成有两种方式:并行 进位和串行进位方式。并行进位加法器设有并行进位产生逻辑,运算速度快;串 行进位方式是将全加器级联构成多位加法器。 全加器的逻辑功能真值表如表 2 中所列。 信号输入端 信号输出端 Ai Bi Ci Si Ci 0 0 0 0 0 0 0 1 1 0 0 1寄存器实验心得(共10篇)docx,寄存器实验心得(共10篇) 通用寄存器实验报告 一、实验目的 1、了解通用寄存器组的用途及对CPU的重要性。2、掌握通用寄存器组的设计方法。二、实验内容 1、通用寄存器组的作用 通用寄存器组是CPU的重要组成部分。集成电路74ls147的真值表需要背吗?如果需要怎么记?试卷 使用编码器74ls147,如何进行对十进制数0编码 3;

Ppt 第三章组合逻辑电路powerpoint Presentation Free Download Id

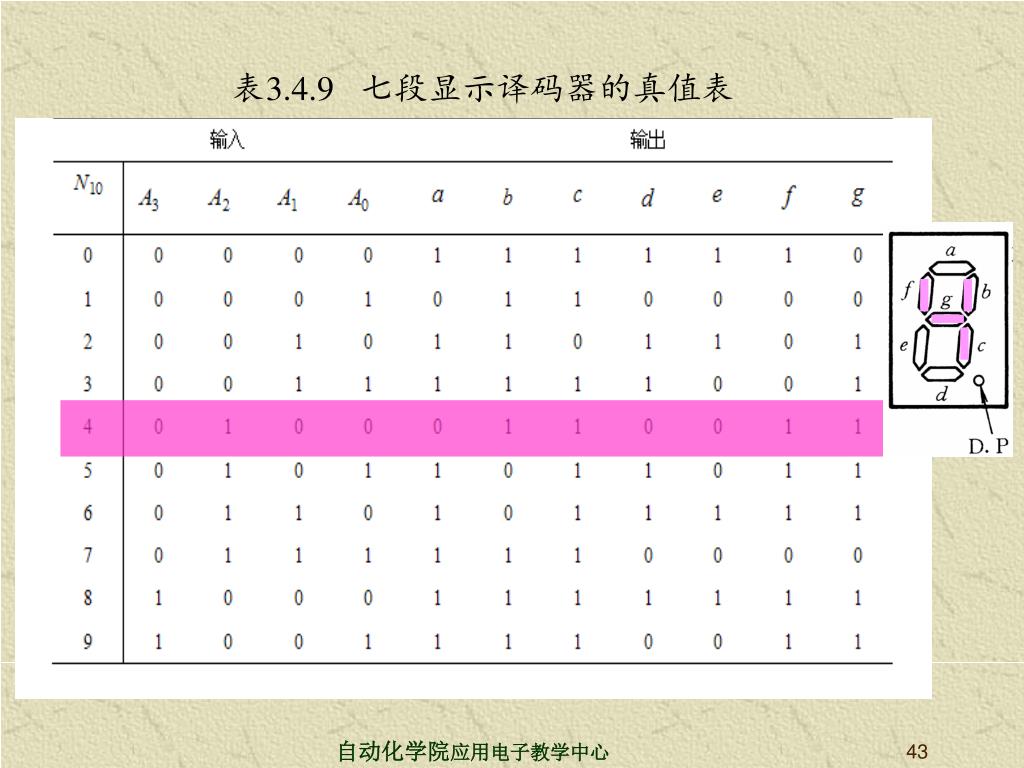

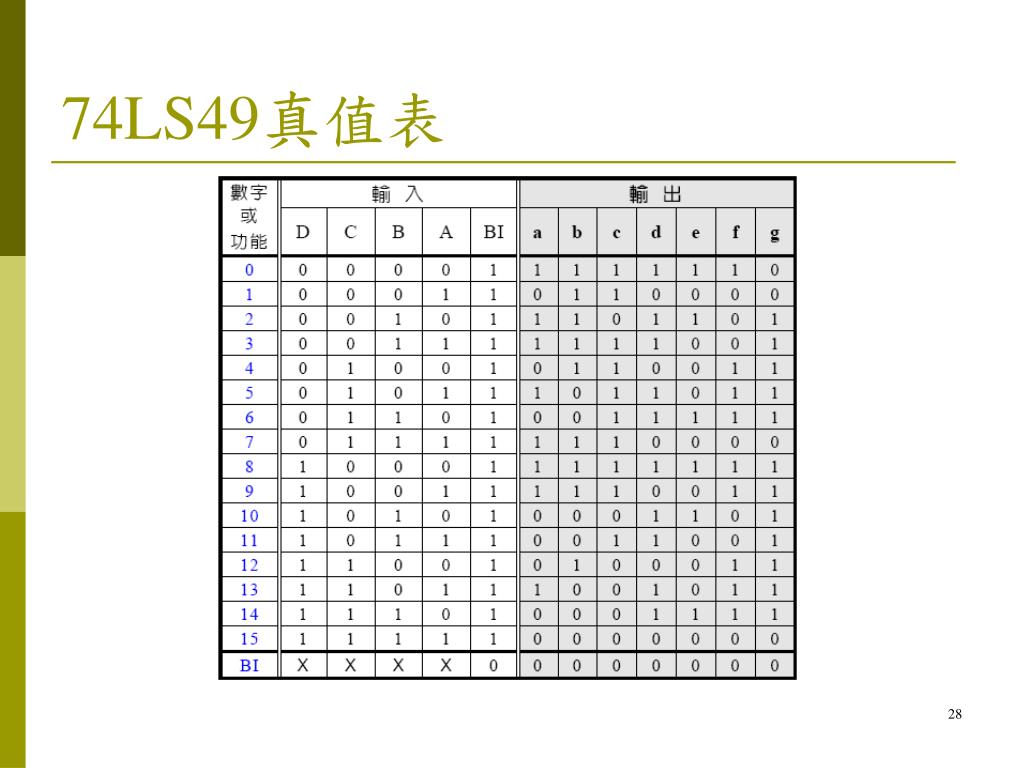

漫談七段顯示器 Jimmyhu

由全减器真值表知: 全减器真值表 同理可知 《数字电子技术基础数字电子技术基础》》 《数字电子技术基础数字电子技术基础》》 题314 分析图p314电路,写出输出z的逻辑函数式,并化简。 cc4512为8选1数据选择器,它的逻辑功能表如表p314所示。实验七 4选1多路选择器设计实验,如何下载 ;实验七 4选1多路选择器设计实验,如何下载 54

电子技术 创元素

Ppt 吳永義powerpoint Presentation Free Download Id

1,数据选择器的定义和功能 数据选择是指经过选择,把 多路数据 中的 某一路 传送到 公共数据线 上,实现数据选择功能的逻辑电路称为数据选择器。 它的作用相当于 多输入的单刀多掷开关 。 2,集成电路数据选择器 常用的集成电路数据选择器有许多种类,并且有coms和ttl产品。真值 : 符号位 X 一般 0 正 1负 负数: 8 二进制8位表示 : 1)真值 X : 1000 2)原码:1 3)反码:1 (符号位不变,其余位 取反 ) 4)补码:1 (符号位不变,最后一位 加一 ) 0 补 = 0 补 = 5)偏置值: 题目 给出 (eg1字长为8位,偏置值为 2∧7 eg2 iee 754 段浮点1 1 0 6 0 1 1 1 1 7 1 1 根据上面的真值表,可以设计出电路图: 将38译码器的输出out(1、2、4、7)作为一个4输入的或门的输入,或门的输出作为加法器的和;将38译码器的输出out(3、5、6、7)作为一个4输入的或门的输入,或门的输出作为加法器的进位输出。

计组实验 P1 Logisim完成单周期处理器开发mips指令集 寒泉 Csdn博客 单周期cpu设计logisim

Ee128a邏輯電路設計實驗 瀏覽老師佈告欄

Ppt 第四章powerpoint Presentation Free Download Id

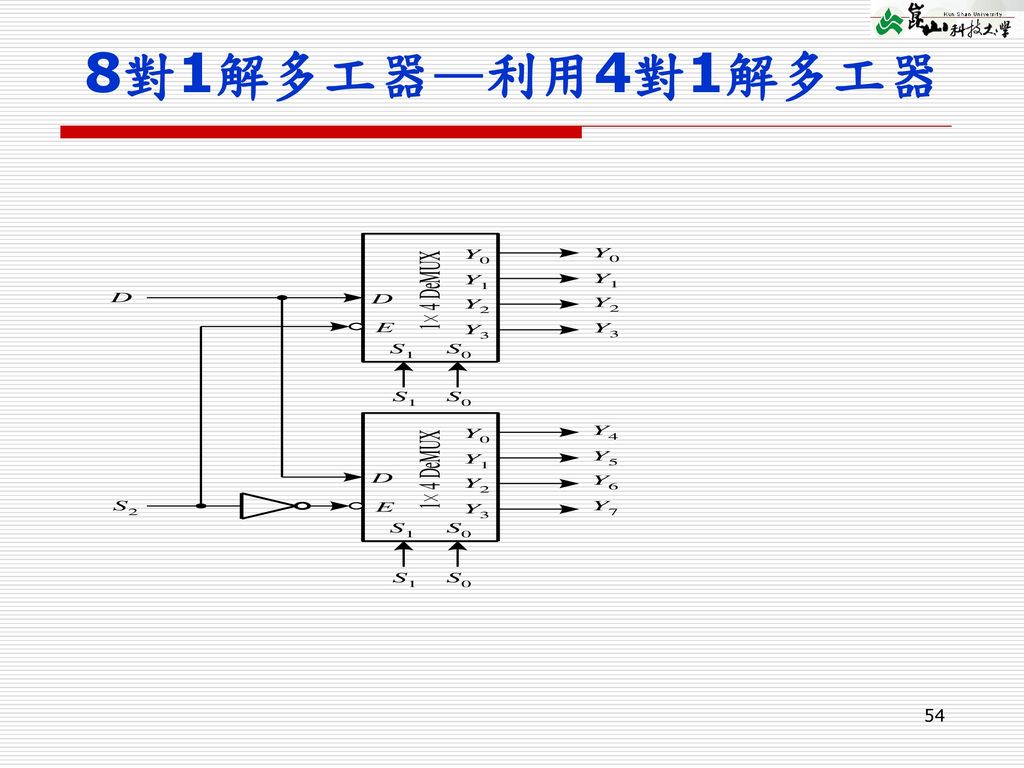

二 相關知識多工器 Multiplexer Mux 或稱資料選擇器 Data Selector 它主要的功能是從許多條資料輸入線 選擇其中一條輸入資料送至單一輸出線上 解多工器 Demultiplexer Demux 的動作和 多工器恰好相反 一般而言 多工器與解多工器是用來執行多段選擇開關的功能

Ppt 第四章資料處理電路powerpoint Presentation Free Download Id

Ppt 數位邏輯實習powerpoint Presentation Free Download Id

Article Info

基于表面肌电的意图识别方法在非理想条件下的研究进展

數位邏輯設計與實習ch04 組合邏輯電路設計 Ppt Download

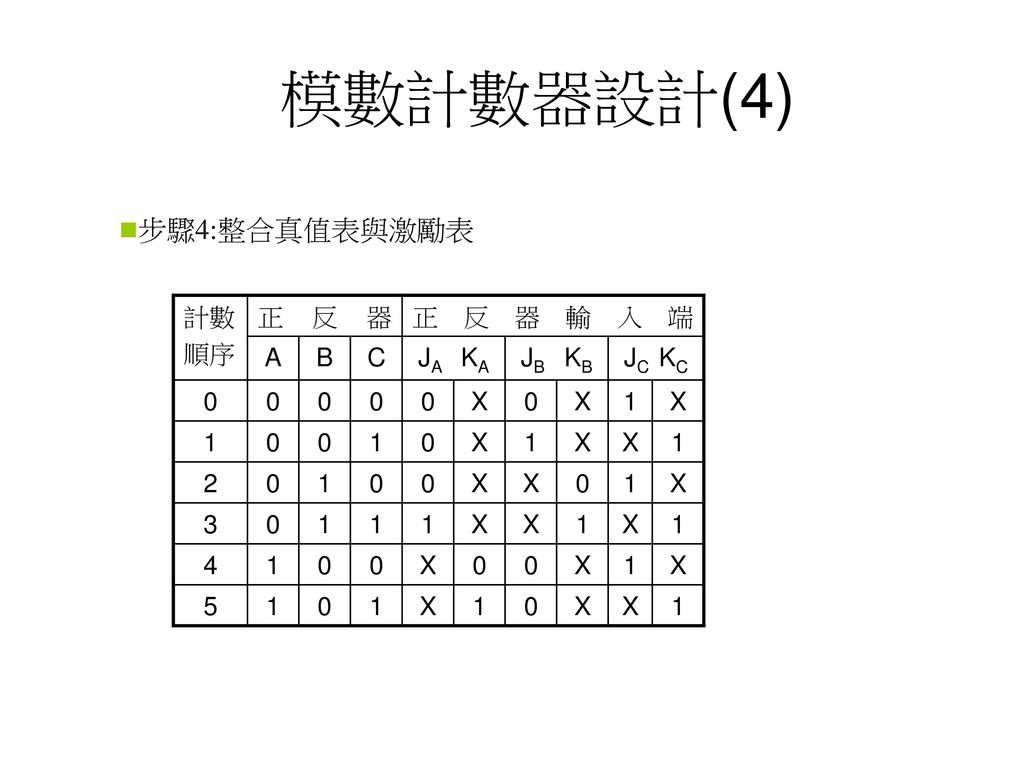

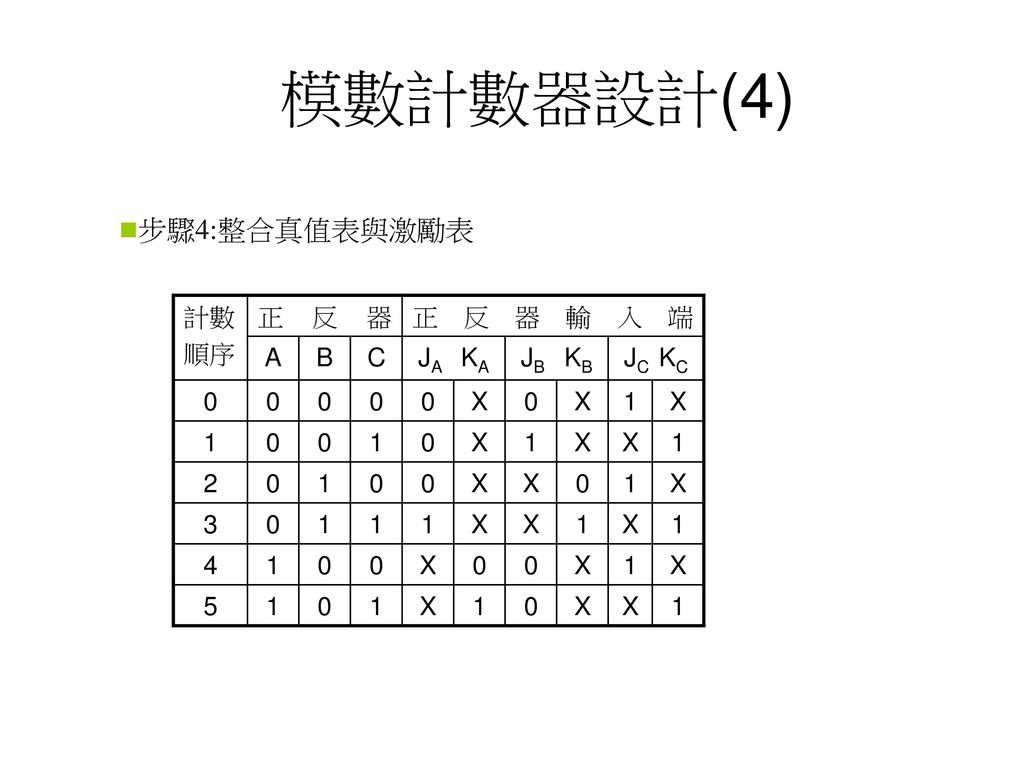

电子电路设计与应用手册第二十三章计数器 分频器

世界第一颗fpga芯片级拆解 详述工作原理 Strongerhuang Csdn博客

Ppt 第四章powerpoint Presentation Free Download Id

Tirqaa95qabykm

Combinational Circuit Ppt Download

数字电路基础知识 六 Fpga的逻辑实现 结构和原理 摆渡沧桑 Csdn博客 Fpga通过什么实现逻辑功能

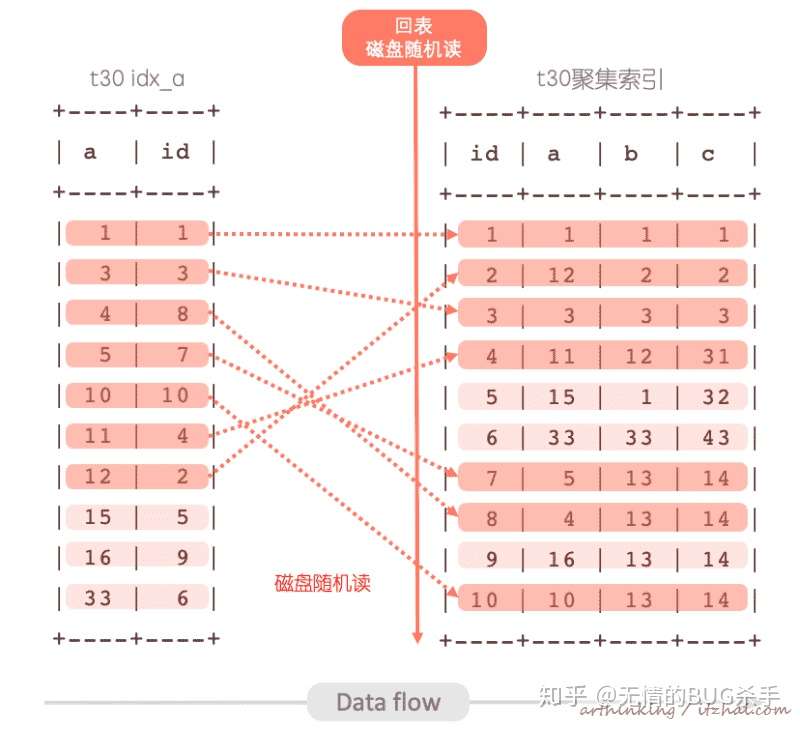

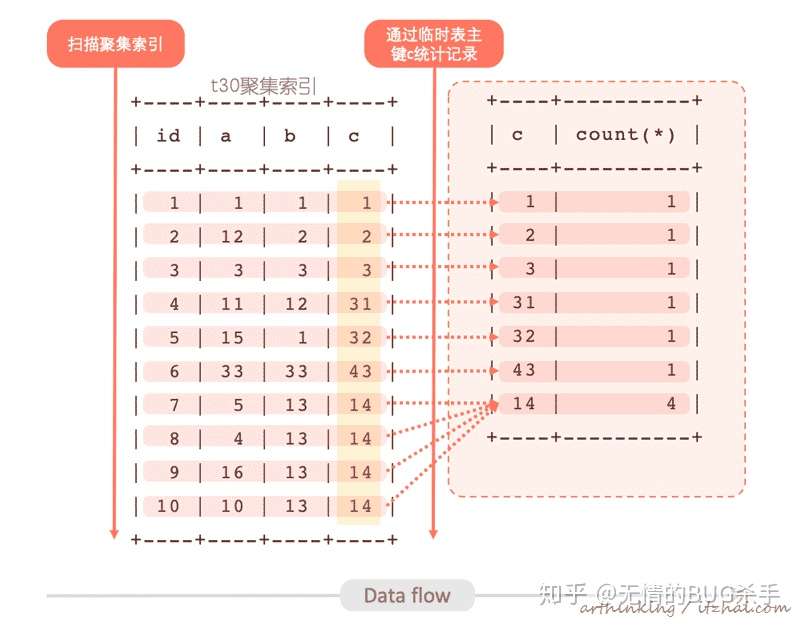

Sql运行内幕 从执行原理看调优的本质 知乎

第6 章組合邏輯電路之設計及應用6 1 組合邏輯電路之設計步驟6 2 加法器及減法器6 3 d加法器6 4 解碼器及編碼器 Ppt Download

Ppt 第四章powerpoint Presentation Free Download Id

掌握 數位邏輯 含實習 複習講義電子試閱本

數位邏輯設計與實習ch04 組合邏輯電路設計 Ppt Download

漫談七段顯示器 Jimmyhu

Tirqaa95qabykm

Article Info

Combinational Circuit Ppt Download

第六章 布林代數 布林代數表示 布林代數基本運算定理 布林代數化簡 Ppt Download

數位邏輯設計與實習ch04 組合邏輯電路設計 Ppt Download

Sql运行内幕 从执行原理看调优的本质 知乎

嵌入式系统基础知识总结 知乎

Ee128a邏輯電路設計實驗 瀏覽老師佈告欄

數位邏輯設計與實習ch04 組合邏輯電路設計 Ppt Download

數位邏輯設計與實習ch04 組合邏輯電路設計 Ppt Download

Ppt 第三章组合逻辑电路powerpoint Presentation Free Download Id

Ppt 第四章powerpoint Presentation Free Download Id

编码器和译码器原理 修改版 下载 Ppt模板 爱问共享资料

Ppt 第四章資料處理電路powerpoint Presentation Free Download Id

0 件のコメント:

コメントを投稿